### Available online at www.sciencedirect.com

# MICROELECTRONICS RELIABILITY

Microelectronics Reliability 45 (2005) 727-732

www elsevier com/locate/microrel

# MOS current divider based PGA

# M. Teresa Sanz \*, Santiago Celma, Belén Calvo, Juan P. Alegre

Área de Electrónica, Departamento Ingeniería Electrónica y Comunicaciones, Facultad de Ciencias, Universidad de Zaragoza, Pedro Cerbuna 12, E-50009 Zaragoza, Spain

Received 21 May 2004; received in revised form 6 September 2004 Available online 6 November 2004

### **Abstract**

A highly linear, digitally programmable gain amplifier (PGA) based on an inherently linear MOS current divider (MCD) is presented in this paper. A 3-bit prototype with a total variation range of 36dB in gain has been implemented in a  $3.3\,V-0.35\,\mu m$  CMOS process with  $2.5\,V$  supply voltage. Experimental results prove the high linearity of the system, which presents distortion levels better than  $-70\,dB$  for  $1\,MHz$  and  $1\,V_{p-p}$  output signals. © 2004 Elsevier Ltd. All rights reserved.

#### 1. Introduction

The presence of a massive digital core in mixed analogue—digital systems results in many complications on the analogue side, such as crosstalk noise contamination of the sensitive analogue signals or voltage supply downscale related issues, among others. Nevertheless, the designer can take advantage of the digital circuitry in the chip to implement high accuracy automatic gain control of the variable gain amplifier and digital tuning of the analogue filter. Digital programmability is thus becoming an essential feature for complex mixed-signal systems. The built-in DSP is often used to accurately compute the control signal for the reconfiguration of the analogue side.

In all these applications, analogue pre-processing of the signal must offer at least the same accuracy as the associated A/D converters. In consequence, for applications over the baseband and telecommunication ranges, a dynamic range of at least  $65 \, dB$  and linearity better than  $-70 \, dB$  are necessary.

Unfortunately, it is not easy to achieve this performance with fully integrated circuits in current CMOS technologies and it becomes even more difficult as the operating frequency increases and supply voltage reduces.

MOS resistive circuits [1–5] show distortion levels higher than  $-60\,\mathrm{dB}$  for  $1\,\mathrm{V}_\mathrm{p-p}$  signal swing in single  $5\,\mathrm{V}$  systems. Furthermore, the tuning capability of this approach is extremely limited for low-voltage systems, as the mechanism of tuning is based on the variation of the gate voltage of transistors operating in the triode region.

For low voltage compatibility, a possible solution is to use programmable arrays of polysilicon resistors and/or capacitors [6]. High linearity and dynamic range have been achieved with this approach. Unfortunately, the maximum operating frequency is limited by the presence of MOS switches in the signal path. Furthermore, extensive area is needed to guarantee a minimum of accuracy [7].

<sup>\*</sup> Corresponding author. Tel.: +34 976761240; fax: +34 976762143.

E-mail addresses: materesa@unizar.es (M.T. Sanz), scelma@unizar.es (S. Celma), becalvo@unizar.es (B. Calvo).

In [8] a programmable gain amplifier (PGA) based on a degenerated differential pair with transconductance enhancement was presented. Even though a good linearity was achieved, its area and power consumption were high because of the use of an interpolated R-2R ladder and  $g_m$ -boosting amplifiers. A PGA based on a source-degenerated differential pair for higher frequency operation was proposed in [9]. Although lower distortion levels than those of similar approaches were achieved by using a linearization technique, linearity is limited by open-loop operation.

An approach combining good linearity and moderate area consumption is the use of MOS transistor configurations which make use of the inherently linear current division principle [10]. This is the case of the PGA presented in [11], where high linearity is achieved. However, the employed active cells limit bandwidth and increase area consumption.

This paper describes the principles, design and experimental results of a highly linear PGA in standard CMOS technology for the low megahertz range. In Section 2 the principle of operation of the PGA, which is based on the inherently linear current division principle, is explained. In order to show the high linearity of the proposed approach, the charge-sheet model [12] is employed. No approximate strong inversion models are used because they suffer from severe limitations when estimating distortion in MOS cells. The MOS resistive circuit [2,3], for example, shows no distortion when analysed with an approximate model in strong inversion. However, when the charge-sheet model is employed, distortion levels in the order of  $-50 \, dB$  for  $1 \, V_{p-p}$  output signal are obtained [13], which agrees with experimental results.

Section 3 describes the proposed PGA. Experimental results are discussed in Section 4 and some conclusions are drawn in Section 5.

# 2. Principle of operation

According to the charge-sheet model, the drain current in a long-channel MOS transistor is given by

$$I_{\rm D} = K[f(\psi_{\rm sL}) - f(\psi_{\rm s0})] \tag{1}$$

with

$$K = \mu C'_{\text{ox}} \frac{W}{I} \tag{2}$$

$$f(\psi_{s}) = f_{1}(\psi_{s}) + f_{2}(\psi_{s}) \tag{3}$$

where

$$f_1(\psi_s) = (V_{GB} - V_{FB})\psi_s - \frac{1}{2}\psi_s^2 - \frac{2}{3}\gamma\psi_s^{3/2}$$

(4)

$$f_2(\psi_s) = (\phi_1 \psi_s + \phi_1 \gamma \psi_s^{1/2}) \tag{5}$$

and where W and L are the channel width and length,  $\mu$  is the carrier effective mobility,  $C_{\rm ox}'$  is the gate oxide capacitance per unit area,  $V_{\rm GB}$  is the gate to bulk voltage,  $V_{\rm FB}$  is the flatband voltage,  $\gamma$  is the body effect parameter,  $\phi_{\rm t}$  is the thermal voltage and  $\psi_{\rm s0}$  and  $\psi_{\rm sL}$  are the source and drain surface potential, respectively. The function  $f_1(\psi_{\rm s})$  corresponds to the drain current component due to drift and the function  $f_2(\psi_{\rm s})$  to the drain current component due to diffusion.

In strong inversion the surface potentials can be defined as:

$$\psi_{s0} \approx V_{SB} + g(V_G, V) \tag{6}$$

$$\psi_{\rm sL} \approx V_{\rm DB} + g(V_{\rm G}, V)$$

(7)

where  $g(V_G, V)$  is a non-linear function of  $V_G - V$ . Furthermore, in strong inversion the current is almost totally due to drift. Thus, introducing (6) and (7) into (4) the drain current in the long-channel MOS transistor is obtained:

$$I_{\rm D} = K[F(V_{\rm G}, V_{\rm D}) - F(V_{\rm G}, V_{\rm S})] \tag{8}$$

where

$$F(V_{G}, V_{X}) = (V_{G} - V_{B} - V_{FB})[V_{X} + g(V_{G} - V_{X})]$$

$$-\frac{1}{2}[V_{X} - V_{B} + g(V_{G} - V_{X})]^{2}$$

$$-\frac{2}{3}\gamma[V_{X} - V_{B} + g(V_{G} - V_{X})]^{3/2}$$

(9)

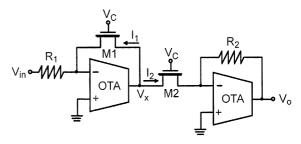

Fig. 1 shows the schematic of a voltage amplifier made using two matched MOS transistors working as a MOS current divider (MCD). Assuming ideal OTAs, i.e., with infinite open-loop transconductance, the drain currents  $I_1$  and  $I_2$  in Fig. 1 are:

$$I_1 = K_1[F_1(V_C, V_x) - F_1(V_C, 0)] = -V_{in}/R_1$$

(10)

$$I_2 = K_2[F_2(V_C, V_r) - F_2(V_C, 0)] = -V_0/R_2$$

(11)

If  $M_1$  and  $M_2$  are perfectly matched,  $F_1(\cdot) = F_2(\cdot)$  and the transfer function of the amplifier is given by

$$\frac{V_{\rm o}}{V_{\rm in}} = \frac{R_2}{R_1} \frac{K_2}{K_1} = \frac{R_2}{R_1} \frac{(W/L)_2}{(W/L)_1}$$

(12)

Fig. 1. MCD based voltage amplifier.

The dependence of  $V_x$  (or  $V_o$ ) on  $V_{\rm in}$  (or  $V_x$ ) is not linear. However, Eq. (12) shows a linear dependence of the output signal  $V_o$  on the input signal  $V_{\rm in}$  [10]. Mismatches in geometry, oxide thickness or mobility influence the accuracy of the gain but do not affect the linearity of the signal in the MCD based voltage amplifier, as inferred from Eq. (12). If there are mismatches in other process parameters such as the body effect coefficient or the flatband voltage,  $F_1(\cdot) \neq F_2(\cdot)$  and distortion arises

Note that (12) shows an expected result.  $V_x$  is a complicated non-linear function of  $V_{\rm in}$ ,  $V_x = f(V_{\rm in})$ , whereas  $V_0$  is another complicated non-linear function of  $V_x$ ,  $V_0 = g(V_x)$ . If transistors  $M_1$  and  $M_2$  are perfectly matched and their operating points are the same,  $f(\cdot)$  is the inverse function of  $g(\cdot)$ ,  $f(\cdot) = g^{-1}(\cdot)$ , except for a proportionality factor. This proportionality factor is the linear gain as expressed in (12).

## 3. MCD based PGA

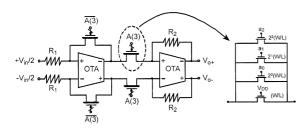

Fig. 2 shows the proposed fully balanced PGA making use of the MCD. In order to reduce both short-channel and mismatch effects, the MOS transistors are biased in the triode region and do not have minimal lengths. We propose the use of wide-band OTAs and banks of MOS transistors in parallel. In this way, the bandwidth can be expanded beyond that of PGAs based on R–2R networks and opamps [14,15]. Complementary words are applied to identical n-bit programmable transistor banks with binary weighted transistor sizes. The differential output voltage  $V_o = V_o^+ - V_o^-$  can be expressed as:

$$\frac{V_{\text{o}}}{V_{\text{in}}} = \frac{\Delta}{1 - \Delta} \frac{R_2}{R_1} \eta$$

with  $\Delta = \frac{1}{[m(2^n - 1) + 2]} \left( 1 + m \sum_{j=0}^{n-1} a_j 2^j \right)$  (13)

Factor  $\eta$  appears as a result of the influence of the finite OTA transconductance value  $G_{\rm m}$ . If  $G_{\rm m}$  is in the order of  $100\,{\rm mA/V}$  for an equivalent load resistance  $R_{\rm L}=10\,{\rm k}\Omega$ , then  $\eta=0.99$ , that is, the OTA works as a wide-band operational amplifier with an error in gain

Fig. 2. Three-bit programmable gain amplifier.  $A(3) = \{a_2 \ a_1 \ a_0\}, \ \overline{A}(3) = \{\bar{a}_2 \ \bar{a}_1 \ \bar{a}_0\}, \ a_i \in \{0, \ V_{\rm DD}\}.$

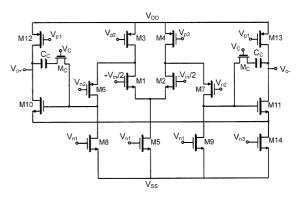

Fig. 3. Scheme of the fully-differential OTA (CMFB circuit omitted).

of 1%. A high transconductance two-stage OTA with resistor-driving capability has been specifically designed as shown in Fig. 3. Although not shown in the figure, a CMFB circuit and a supply independent biasing circuit have been used [16].

The gain setting resolution of the PGA is given by the word length n and the factor m, which is the size ratio between transistors  $M_{a0}$  and  $M_a$ , i.e.,  $m = (W/L)_{a0}/(W/L)_a$ .

Note that the voltage gain given by (13) is approximately exponential for the central word values. For instance, for a total variation range of  $36 \,\mathrm{dB}$  (m=1, n=3,  $R_2/R_1=3$ ) the gain increases linearly on a dB-scale over a 20 dB range with a maximum gain deviation from exponential behaviour of  $0.36 \,\mathrm{dB}$ . Outside the central region the rate of change in gain is even faster, which provides even better control of the output voltage in comparison to a simple exponential gain characteristic [17]. The PGA is thus characterized by its inherently high linearity and wide range in gain, which can be digitally programmed without affecting the dynamic range and THD. Resistors  $R_1$  and  $R_2$  are implemented with high resistivity polysilicon and their values must be chosen so as to moderately load the OTA.

# 4. Experimental results

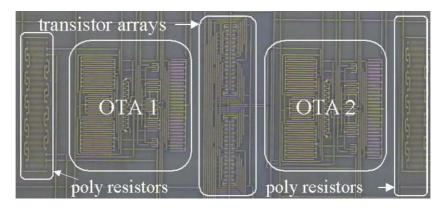

To verify the former analysis, a 3-bit PGA with m = 1 was integrated in 0.35  $\mu$ m technology and measurements were performed on the circuit. Detail of the chip is shown in Fig. 4.

For all measurements the PGA was driven by a single-ended-to-balanced voltage converter and the differential output voltage was converted to a single output voltage. Both input and output converters were based on high performance AD844 current feedback opamps, which exhibit 60 MHz bandwidth and non-linear distortion lower than  $-86\,\mathrm{dB}$ . Distortion measurements at

Fig. 4. Chip microphotograph (90 μm × 280 μm).

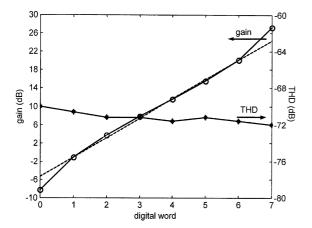

Fig. 5. (O) Gain setting  $(n = 3, m = 1, R_f/R_1 = 3)$  and (\*) THD (1 MHz @ 1 V<sub>p-p</sub> output signal) for each control word.

Fig. 6. (\*)Experimental THD (1 MHz @ 1  $V_{p-p}$  output signal) for each gain setting and simulated results with ( $\bigcirc$ ) the BSIM3v3 and ( $\square$ ) the *charge-sheet* model.

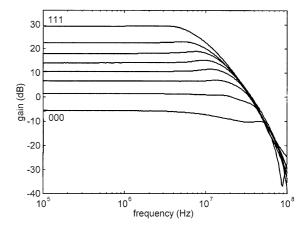

Fig. 7. Frequency response for each gain setting  $(n = 3, m = 1, R_f/R_l = 3)$ .

1 MHz were challenging, as test signals provided by the signal generator showed higher residual distortion than those meant to be measured. A simple technique for high frequency low distortion measurements was employed [18].

Table 1 Three-bit PGA performance

| Three on Torr performance               |                                     |  |

|-----------------------------------------|-------------------------------------|--|

| Parameter                               | Value                               |  |

| CMOS technology                         | 0.35 μm                             |  |

| Supply voltage                          | 2.5 V                               |  |

| Gain setting                            | −8 to 28 dB                         |  |

| Maximum gain error                      | $0.27\mathrm{dB}$                   |  |

| Bandwidth                               | 16 MHz                              |  |

| Area                                    | $0.025\mathrm{mm}^2$                |  |

| Quiescent power                         | $8\mathrm{mW}$                      |  |

| Settling time (1–99%)                   | 30 ns                               |  |

| THD (1 MHz @ 1 V <sub>p-p</sub> output) | $-70\mathrm{dB}$                    |  |

| Input referred noise @ {111}            | $50 \mathrm{nV}/\sqrt{\mathrm{Hz}}$ |  |

Table 2 Performance comparison of PGAs

|                         | Rijns [8]   | Elwan et al. [11] | Calvo et al. [9] | This work   |

|-------------------------|-------------|-------------------|------------------|-------------|

| CMOS technology (µm)    | 0.8         | 1.2               | 0.35             | 0.35        |

| Supply voltage (V)      | 5.0         | 3.2               | 3.3              | 2.5         |

| Gain range (dB)         | 14 (3 bits) | 25 (6 bits)       | 16 (3 bits)      | 36 (3 bits) |

| Bandwidth (MHz)         | 15          | 4.1               | 250              | 16          |

| THD (dB)                | $-65^{a}$   | $-68^{b}$         | $-60^{c}$        | $-70^{a}$   |

| Quiescent power (mW)    | 25          | 2.3               | 1.95             | 8           |

| Area (mm <sup>2</sup> ) | 0.175       | 0.442             | 0.010            | 0.025       |

<sup>&</sup>lt;sup>a</sup> 1 MHz @ 1 V<sub>p-p</sub> differential output signal.

Fig. 5 shows the gain setting and THD (1 MHz @ 1  $V_{p-p}$  output signal) of the PGA for each digital word. It can be seen that dB-gains are approximately equally spaced for the central words and move away from this tendency for the words  $\{000\}$  and  $\{111\}$ . This is due to the fact that, as already mentioned, (12) is not exactly an exponential function but an approximation to it. The linearity of the whole system remains very high over the whole amplification range, as distortion levels obtained are better than  $-70\,\mathrm{dB}$  for a 1 MHz and  $1\,V_{p-p}$  output signal for every gain.

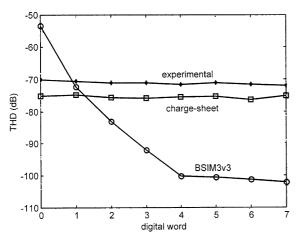

As explained in Section 2, distortion is mainly due to mismatches in the threshold voltage of the transistors which constitute the MCD. In the actual  $0.35\,\mu m$  process, a standard deviation of the threshold voltage  $\sigma(\Delta V_i) = 4.7\,mV$  was reported by foundry for these transistors. Fig. 6 shows the simulated THD (1 MHz @ 1  $V_{p-p}$  output signal) for each gain setting considering the given  $\sigma(\Delta V_i)$  and employing both the BSIM3v3 model provided in the design kit of the technology and the *charge-sheet* model. It is shown that the BSIM3v3 model does not fit in with experimental results. The charge-sheet model, on the contrary, fairly approaches the measured results.

The standard deviation of factor K,  $\sigma(\Delta K/K) = 0.4\%$ , only affects gain accuracy. A maximum gain error of 0.27 dB was measured.

Fig. 7 shows the frequency response for each word. Table 1 shows the measured performance summary of the integrated circuit. In Table 2 the performance of the proposed PGA is compared to three previous realizations in CMOS technology [8,9,11]. It is worth noting that the MOS Current Divider based PGA achieves the lowest distortion level. It also shows the best trade-off between bandwidth, non-linear distortion and power consumption.

# 5. Conclusions

In this paper, an approach to designing highly linear CMOS PGAs has been proposed that takes advantage of the inherently linear current division principle. Experimental results for a 3-bit PGA confirm the feasibility and good performance of the proposed technique. A dynamic range better than 65 dB is achieved, so these programmable cells are suitable for use in analogue front-end (AGC and filtering) for 10-bit accuracy digital systems fabricated in standard CMOS technologies.

# Acknowledgement

This work has been partially supported by the DGA (P078/2001), CICYT (TIC02-00636) and DGA (B002/2000).

## References

- Tsividis Y, Banu M, Khoury J. Continuous-time MOS-FET-C filters in VLSI. IEEE J Solid-State Circ 1986; 21(1):15-30.

- [2] Czarnul Z. Novel MOS resistive circuit for synthesis of fully integrated continuous-time filters. IEEE Trans Circ Syst 1986;33(7):718–21.

- [3] Song B-S. CMOS RF circuits for data communications applications. IEEE J Solid-State Circ 1986;21(2):310–7.

- [4] Moon U-K, Song B-S. Design of a low-distortion 22-kHz fifth-order Bessel filter. IEEE J Solid-State Circ 1993; 28(12):1254-64.

- [5] Vavelidis K, Tsividis Y. R-MOSFET structure based on current division. Electron Lett 1993;29(9):732–3.

- [6] Durham AM, Redman-White W, Hughes JB. Highlinearity continuous-time filter in 5-V VLSI CMOS. IEEE J Solid-State Circ 1992;27(9):1270–6.

- [7] Alzaher HA, Ismail M. Digitally tuned analogue integrated filters using R-2R ladder. Electron Lett 2000;36(15): 1278-80.

- [8] Rijns JJF. CMOS low-distortion high-frequency variablegain amplifier. IEEE J Solid-State Circ 1996;31(7):1029–34.

- [9] Calvo B, Celma S, Sanz MT. CMOS digitally programmable cell for high-frequency amplification and filtering. In: Proceedings of the IEEE International Symposium on Circuits and Systems 2004 (ISCAS'04), p. I-421–4.

- [10] Bult K, Geelen GJGM. An inherently linear and compact MOST-only current division technique. IEEE J Solid-State Circ 1992;27(12):1730–5.

<sup>&</sup>lt;sup>b</sup> Conditions not specified.

$<sup>^{</sup>c}$  100 kHz @ 0.4  $V_{p-p}$  differential output signal.

- [11] Elwan HO, Ismail M. Digitally programmable decibellinear CMOS VGA for low-power mixed-signal applications. IEEE Trans Circ Syst II 2000;47(5):388–98.

- [12] Tsividis Y. Operation and modeling of the MOS transistor. second ed. McGrawHill; 1999.

- [13] Flandre D, Jespers P. Charge-sheet modelling of MOS I-V fundamental nonlinearities in MOSFET-C continuoustime filters. Electron Lett 1995;31(17):1419–20.

- [14] Celma S, Sabadell J. A low-distortion digitally programmable continuous-time filter and variable-gain amplifier. In: Proceedings of the 26th European Solid-State Circuits Conference 2000 (ESSCIRC'2000). p. 256–9.

- [15] Pun K-P, Choy C-S, Chan C-F, da Franca JE. Digital frequency tuning technique based on current division for integrated active RC filters. Electron Lett 2003;39(19):1366–7.

- [16] Razavi B. Design of analog CMOS integrated circuits. New York: McGraw-Hill; 2001.

- [17] Harjani R. A low-power CMOS VGA for 50 Mb/s disk drive read channels. IEEE Trans Circ Syst II 1995;42(6): 370-6.

- [18] Celma S, Aldea C, Sabadell J, Martínez PA. A technique for high frequency low distortion measurements. In: IEEE Instrumentation and Measurement Technology Conference 1998;728–31.